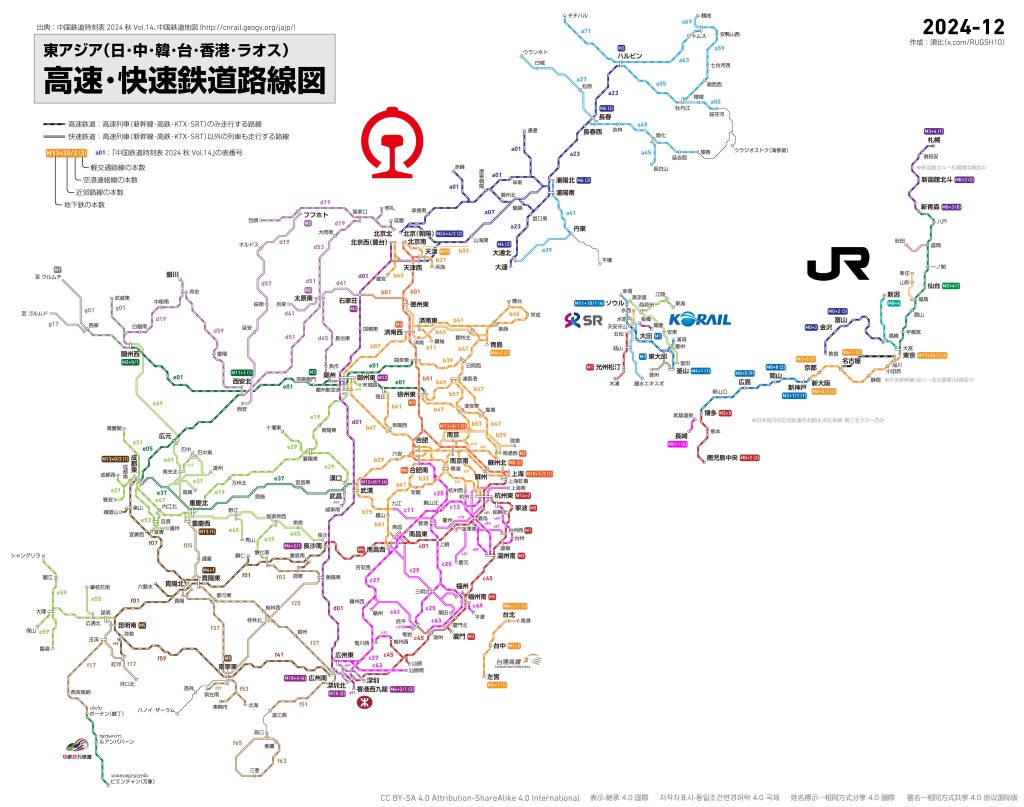

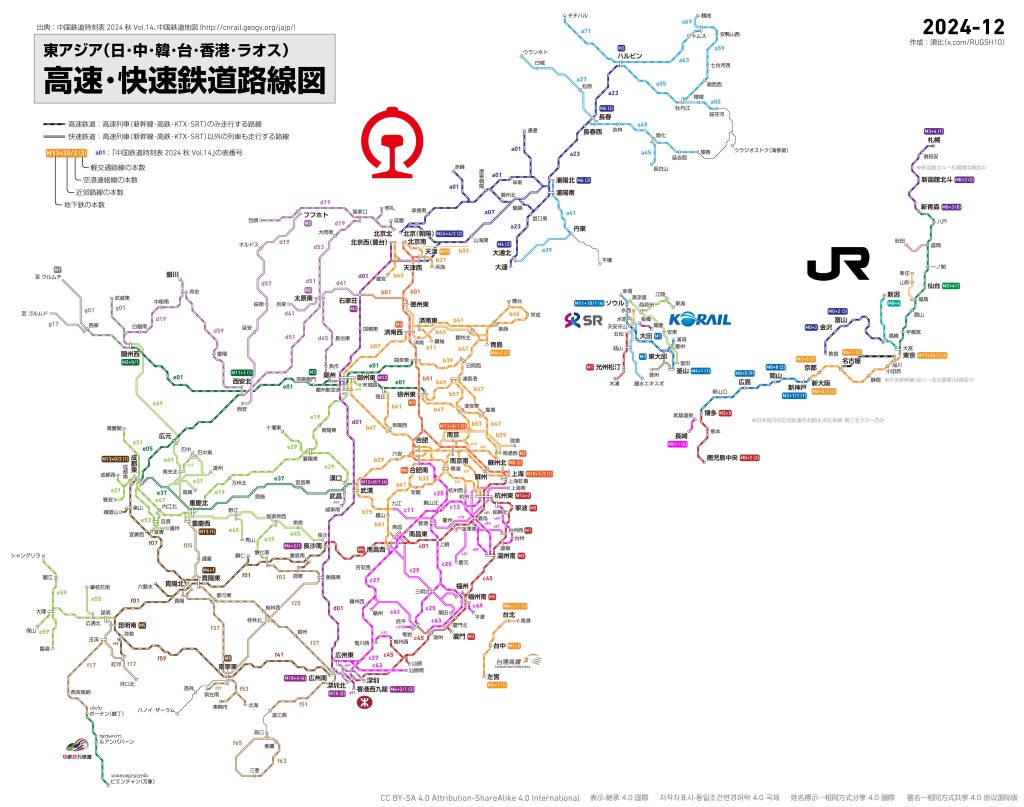

ref. https://x.com/RUGSH10/status/1913169747929387480/photo/1

蒐集一些看過的資訊,不代表本人立場

ref. https://x.com/RUGSH10/status/1913169747929387480/photo/1

在台灣這叫關廁所,也是很多駕駛右轉的時候會做的事情,避免機車從右側超車

閱讀全文〈原來日本人會教人轉彎時擋住腳踏車的行進路線〉後有台達澄清新聞稿

閱讀全文〈[PTT] 台達電人資和主管聯手霸凌勞工真實事件簿〉ref.

https://www.capitancreative.com/wreck/wreck4/%E4%B8%89%E5%92%8C%E5%85%84%E5%BC%9F%E8%BC%AA.html