原文 : AI in Chip Design: from Basic Tools to LLMs and AI Agents

by Bryan Chin, Jishen Zhao, Haoxing (Mark) Ren, Stelios Diamantidis, Hans Bouwmeester, Hanxian Huang on Oct 16, 2024 | Tags: AI Agents, Chip Design, Large Language Models

新的硬體能力使許多產業和應用中的轉型 AI 技術成為可能。其中一個產業就是硬體設計本身,這正是最初使 AI 能力增強的學科。在 2024 年的 Hotchips 大會上,我們舉辦了一場教程,概述了影響我們設計晶片的轉型 AI 技術。這篇部落格文章提供了該教程的簡要總結。

教程概述

計算機架構社區擁有豐富的歷史,設計晶片的方法和工具隨著時間的推移而演進。最近,像 Google 和 Nvidia 這樣的公司展示了在晶片設計方法中整合尖端 AI 的成果。因此,在討論今年 HotChips PC 會議的主題時,我們決定專注於 AI 如何開始影響處理器設計(更廣泛地說是數位晶片設計),以及這些能力如何在不久的將來演變以重塑晶片設計實踐。

該教程分為幾個部分,按照 AI 在晶片設計中的發展順序:晶片設計中的使用AI 的歷史 、大型語言模型 (LLM) 背後的基本概念、LLM 的應用、檢索增強生成 (RAG) 和晶片設計 AI 代理。一般來說,AI 可以用來探索極大的設計空間。在設計晶片時,工程師通常面臨許多選擇和限制。設計空間包括邏輯、面積、單元庫、製程參數、EDA 工具選擇和配置的權衡。AI 可以幫助設計師探索設計空間並整合領域特定知識。

分析、優化與輔助

專門針對晶片設計的 AI 技術可以分為三大類:分析、優化 和 輔助。

分析 涉及利用 AI 解釋與晶片設計相關的數據,使設計師能夠對晶片的實現方式做出選擇。一個例子是分析時序或佈局佈線工具的輸出,以了解是否滿足特定的性能、功耗或面積目標。

優化 工具可以利用 AI 基於指定約束來改進設計。例如,AI 技術可以應用於邏輯綜合或單元佈置,以探索眾多設計解決方案。

設計輔助 在設計的多個階段幫助設計師,例如從圖表創建 RTL、創建文檔或指導設計空間探索以進行優化。

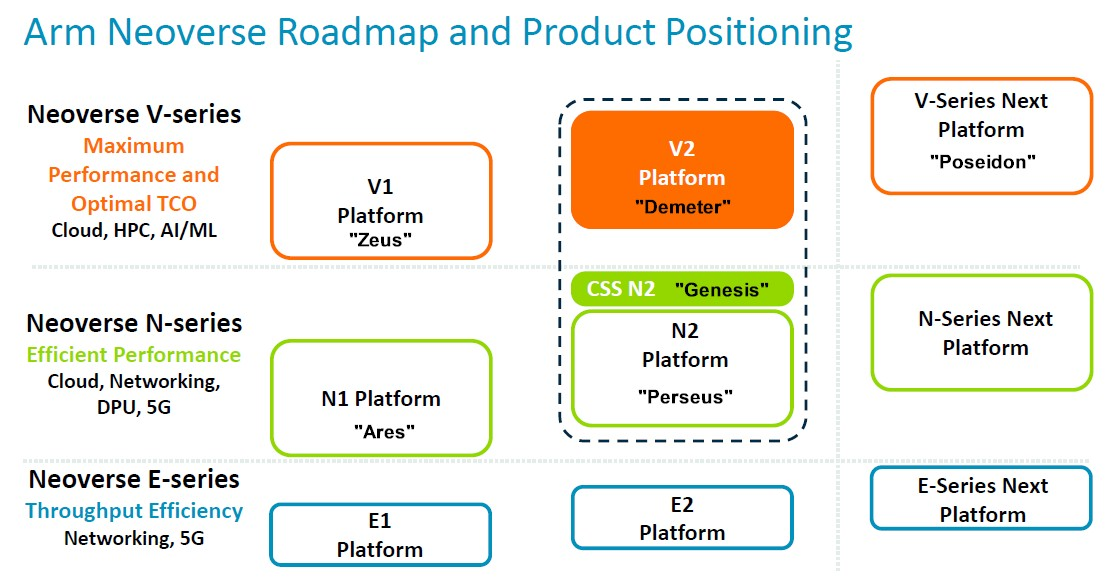

Figure 1 : Development of Analysis, Optimization and Assistance Tools at NVIDIA

如圖 1 所示,這些用例隨著時間的推移而演變,Nvidia 就是一個很好的例子。同樣,隨著時間的推移,AI 承擔的設計任務的複雜性也在增加。時鐘樹優化之類的搜索空間可能約為 10^4 種可能性,而考慮面積、靜態和動態功耗、延遲、頻寬和製程的記憶體生成器可能考慮 10^25 左右的狀態空間。

分析

深度學習技術,如卷積神經網路 (CNN) 和圖神經網路 (GNN),在分析方面非常有效。這兩種技術都適用於大型數據集,這在physical layout數據庫或netlist中很常見。例如,估計晶片上電源網路的 IR 掉電可能是一項計算密集型任務。在 MAVIREC 中,AI 模型獲取晶片的功耗圖,並用於以秒為單位估計 IR 掉電,而傳統 EDA 方法需要數小時。

優化

計算機長期以來一直用於優化晶片設計,傳統 AI 技術用於某些優化任務。在貝葉斯優化(Bayesian optimization)中,模型用於估計目標功能的值及其不確定性,隨後將模型的輸出饋入目標功能進行評估。估計黑盒功能的能力可以應用於各種晶片優化問題。例如,在 AutoDMP 中,目標功能旨在優化標準單元佈置的線長、擁塞和密度。在這種情況下,來自商業 EDA 工具貝葉斯優化(Bayesian optimization)技術用作實際標準單元佈置結果的計算成本較低的代理。

強化學習 (RL) 技術涉及使用 AI 生成潛在實現並向 AI 工具提供反饋以強化更好的解決方案。RL 演算法使用反饋來學習輸入參數與它們對結果的影響之間的關係。使用 RL 工具的一個例子是修復physical layout中的設計規則檢查 (\design rule check, DRC) 錯誤。在 NVCell 中,RL 工具學習修復設計規則檢查器發現的設計規則違規。在教程中,我們展示了一個示例,其中工具學習向 physical layout 添加 metal 0 以消除違規的設計規則。

第二個示例使用 RL 創建最佳前綴加法器。前綴加法器可以有多種設計變體。每種變體可能具有不同的時序、功耗和面積特性,基於物理設計屬性(例如線阻、可路由性、擁塞等)。在 PrefixRL 中,機器取代人類直覺,生成人類設計師可能想不到的前綴加法器設計。結果是比眾所周知的前綴加法器架構更優化的設計。

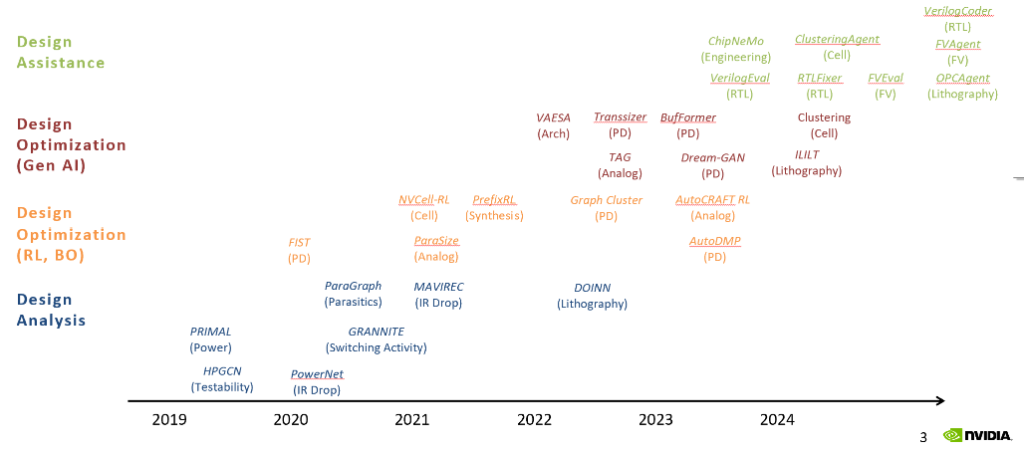

第三個使用 RL 進行晶片設計的示例是優化功耗、性能和面積 (PPA)。在這種情況下,RL 考慮多個目標——Leakage、Timing 和設計規則——並探索設計選項、工具選擇、工具參數和 library cell 選項。如圖 2 所示,RL AI 工具實現了比手動優化設計更好的結果(更低功耗、更快)。

Figure 2. AI-Assisted Design Search

基於 RL 的技術的一個可能缺點是它們依賴於潛在昂貴的設計評估。例如,評估特定單元佈置的有效性可能需要運行各種 physical design 工具,extracting timing、面積和寄生信息以得出 timing、功耗和面積成本。

輔助

輔助的想法是使用 AI 幫助工程師執行涉及高維輸入的高級設計相關任務,這些輸入代表設計權衡。基於這些輸入計算輸出的“成本”可能計算成本很高。因此,如果不使用一些估計技術,自動探索設計空間可能不切實際。傳統上,人類直覺、經驗和高級模擬模型用於確定“最佳”設計。然而,AI 軟體可以估計哪些設計更有可能以更低的計算成本接近最優性,而不是運行實際模擬。

具有潛在高成本評估的大型設計空間的一個示例是 logic synthesis。在 RTL 闡述之後,使用計算成本高昂的綜合和佈局佈線工具來評估結果的 PPA。在 FastPASE 中,圖卷積網路 (GCN) 用於在邏輯綜合之前估計給定 RTL 設計的 PPA。結果是評估速度提高了 10 倍。

大型語言模型與晶片設計

大型語言模型 (LLM) 的近期流行對許多學科產生了巨大的影響。自 ChatGPT 和其他 LLM 公開可用以來,人們已將其應用於眾多不同的應用中。從根本上說,LLM 在文本序列(token)上進行訓練。這些模型嘗試根據prompt(給定的輸入模式)預測後續token。迄今為止,這些模型已在自動生成軟體等應用中取得了相當高的成功。

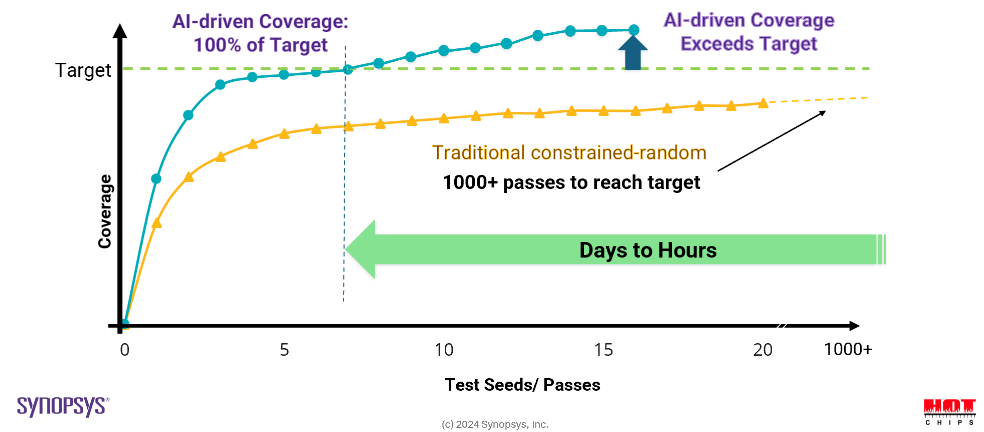

類似於使用 LLM 生成軟體,也可以使用 LLM 生成硬體描述語言 (HDL) 如 System Verilog 中的設計。類似的用例包括生成 testbenches 或 EDA 腳本。在測試平台生成用例中,LLM 用於生成 constrained random tests 以進行 RTL 驗證。與傳統方法相比,目標覆蓋率可在更少的模擬和更短的時間內實現,如下圖 3 所示。

Figure 3: Enabling Faster Time to Closure

同樣,LLM 可以用於生成 EDA 工具的腳本。例如,在 ChipNeMo 中,LLM 的任務是生成 EDA 腳本,以收集晶片特定區域中的 flip-flops 數量並識別與特定電路相關的邏輯。設計師可以使用自然語言提示,例如“在 TOOL1 中編寫代碼以打印矩形 (0, 0, 100, 100) 中的觸發器數量”或“編寫 TOOL2 tcl 過程以查找從‘$pinA’到‘$pinB’的相交邏輯”。

檢索增強生成 (RAG)

LLM 可以用於增強對現有數據的訪問。例如,複雜的晶片設計方法通常包含大型錯誤數據庫。LLM 可以用於生成對數據庫的查詢,而無需對錯誤數據庫的內容進行明確訓練。

RAG 還可以用於閱讀特定 RTL IP 的庫文檔,然後生成組件之間的模組連接。例如,用戶可能會要求 RAG 模型“為連接 AXI-APB 橋 IP 和 RTC IP 的模組提出頂層 Verilog”。然後,模型訪問 AXI-APB IP 和 RTC IP 的一些文檔並生成 Verilog 模組介面。請注意,LLM 並沒有針對該庫進行特定訓練,而是將其用作外部來源。

在專門領域(如晶片設計)中使用通用 LLM 的想法屬於領域自適應 LLM 的範疇。在此框架中,通用 LLM 與特定領域的知識相結合。例如,EDA 供應商可以提供一個 LLM,該 LLM 具有通用的晶片設計知識和工具,供客戶用其專有 IP 特定數據來增強該模型。例如,在 RTLFixer 中,LLM 訪問人類專家 Verilog 知識的數據庫,以更好地修復 RTL 語法錯誤。結果是比一次性方法更高質量的自動生成 RTL 代碼。

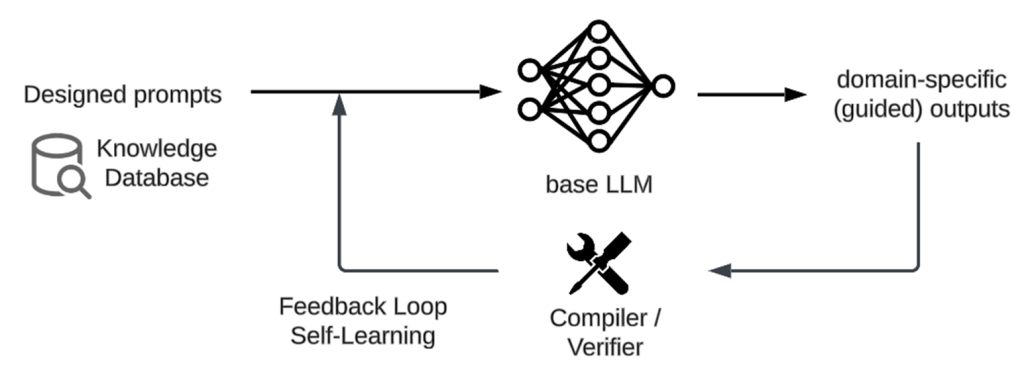

領域自適應 LLM 技術可以根據它們在模型預訓練、微調或推理階段的應用階段進行分類。在預訓練階段整合大規模領域數據將從頭開始創建領域特定的 LLM。或者,我們可以改用基礎 LLM 並使用特定任務的領域數據對其進行微調,以使通用 LLM 適應特定領域的任務。最後,在推理階段,領域知識可以通過提示工程、代理或 RAG 技術(如 RTLFixer 中所用)饋入模型。圖 4 說明了領域自適應推理的過程。鑑於這些選項,一個開放的研究問題是如何在各種晶片設計任務中選擇這些領域自適應技術。

Figure 4: Domain-Adaptive Inference Loop

AI 代理

隨著使用 AI 進行晶片設計的領域發展,更複雜的任務變得可行。一個有前景的領域是使用 AI 代理。AI 代理的基本思想是通過整合多個代理來整合資源,每個代理可能具有不同的專業知識。代理還可以使用工具——例如,LLM 通常不太擅長數學,但 LLM 代理可以學會使用計算器進行數學運算。同樣,代理可以學會使用各種 EDA 工具以及與其他代理交互。

每個級別的代理都可以用於實現流程的部分。在 ChatDev 中,不同的代理在生成軟體的過程中執行不同的功能(CEO、CTO、審閱者、測試人員、程式員)。這些代理相互交互以執行整體任務。

類似的代理組織可以應用於晶片設計任務。例如,多個代理可以用於從高級規格生成 RTL 代碼,如 VerilogCode 所做的那樣。一個代理可以負責高級任務規劃,生成詳細的任務規格,例如需要哪些模組、每個模組的功能以及模組的輸入和輸出。然後,第二個代理可以根據這些規格生成 Verilog 代碼。第三個代理可用於測試和調試設計。所有代理都可以使用外部工具(例如佈局規劃器、 logic synthesis 工具、timing 工具等)。

結語

晶片設計的任務包含複雜的權衡和領域特定知識。過去曾將 AI 用於晶片設計過程的部分。最近,AI 在更高級別的複雜任務中找到了更多應用。分析、優化和輔助的廣泛類別代表越來越困難的任務。隨著 AI 的發展,我們開始看到 AI 在許多不同且複雜的晶片設計任務中的應用。在本文中,我們僅簡要描述了 AI 影響晶片設計的一些領域。鼓勵感興趣的讀者訪問 HotChips 觀看完整教程並訪問相關材料(對於未參加會議的人,視頻和材料將在 2024 年 12 月提供給非與會者)。我們希望該教程能夠激發對晶片設計中 AI 的更廣泛認識,並激發該領域的新想法和應用。