ref. https://www.facebook.com/photo/?fbid=2315928868826955&set=g.185427322881021

閱讀全文〈台中大雅交流道舊照〉台中舊衛道中學遊樂園照片

不要給她鏡頭

陳聖文對楊智伃說的

因為王喜歡年幼的女孩

異世界默示錄麥諾格拉-從毀滅文明開始征服世界 S01E06

盡你所能地把所有的小女孩都找過來

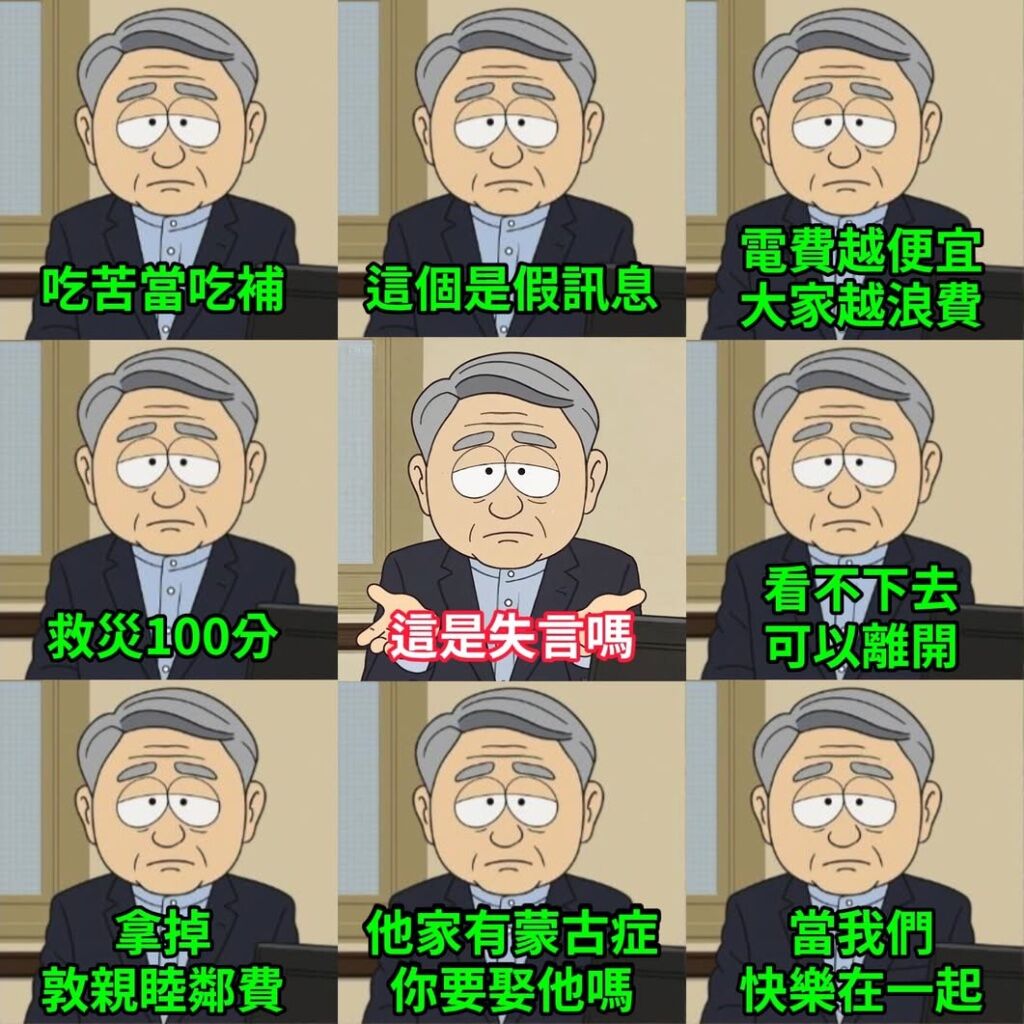

經濟部長郭智輝名言集

戰場上士兵短兵相接的節奏

知乎的精彩答案,備份一下

這跟俄烏戰爭的節奏很不一樣

作者是法外

士兵只携带150发子弹,战场上打光了怎么办? – 逆水的回答 – 知乎

https://www.zhihu.com/question/622363261/answer/1931755600800355666

中國大陸網路動漫黑名單

[PTT] 罷免舞

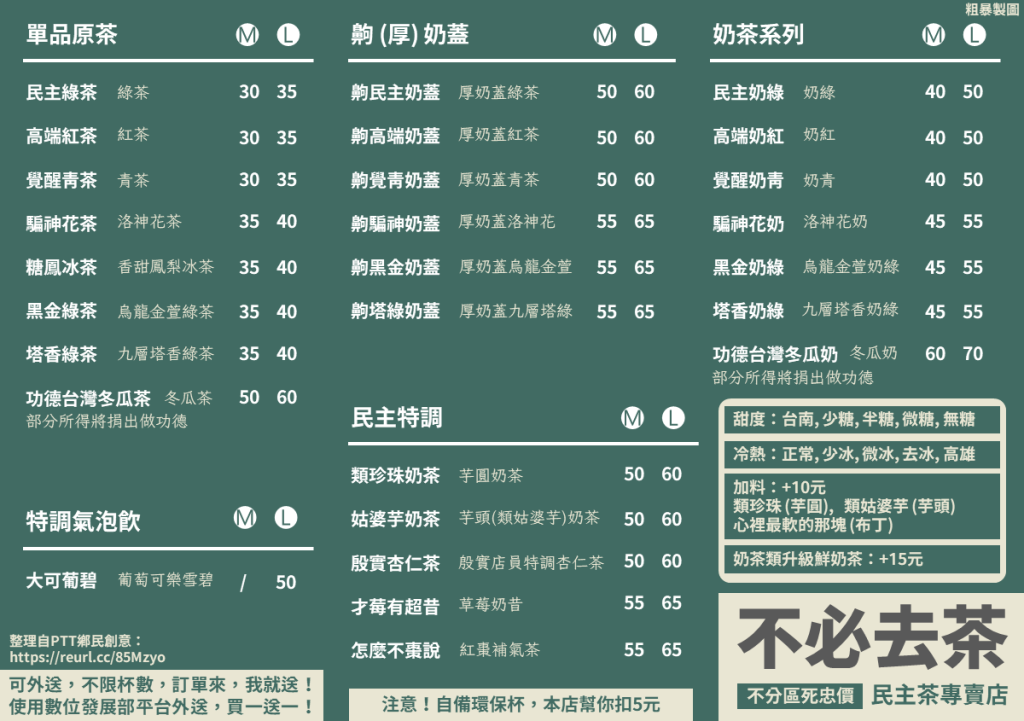

不必去茶 民主茶專賣店

ref. https://www.pttweb.cc/bbs/Gossiping/M.1672975498.A.2D7

2025 中央地方租金爭議

對於租金補貼經費由地方共同分擔這件事,今天在立法院有許多委員質詢,我也接到幾通記者的電話訪問,明天應該會上節目談這題,乾脆先在臉書說清楚,也整理一下論述思緒。

簡單來說,這件事就是「中央請客,地方買單」。雖然內政部不斷強調不是這樣,但這只是內政部一貫的話術,容我細細講來,文章會滿長的。